SK Hynix devient la première entreprise à achever le développement de puces mémoire HBM4 et à préparer la production de masse pour les systèmes d'IA

SK Hynix franchit le mur de la mémoire : Les premières puces HBM4 prêtes pour le prochain champ de bataille de l'IA

Le géant sud-coréen de la mémoire annonce une percée architecturale qui pourrait remodeler l'économie des centres de données alors que la demande en IA explose

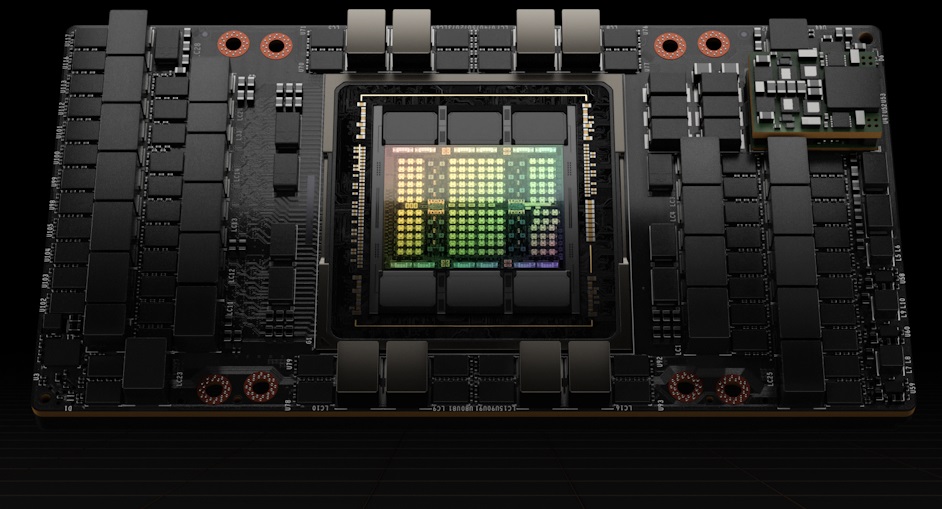

SK Hynix a achevé le développement des premières puces mémoire HBM4 au monde, marquant un moment charnière dans la course effrénée pour satisfaire l'appétit insatiable de l'intelligence artificielle en bande passante de données. L'annonce, faite mercredi depuis Séoul, positionne l'entreprise pour s'emparer de la part du lion d'un marché que les analystes estiment à plus de 15 milliards de dollars d'ici 2030.

Cette avancée intervient alors que les centres de données d'IA sont mis à rude épreuve par ce que les ingénieurs appellent le « mur de la mémoire » – un goulot d'étranglement fondamental où la puissance de traitement dépasse largement la bande passante de la mémoire. La HBM4 de SK Hynix promet de briser cette contrainte avec une largeur de bus doublée à 2 048 bits et des vitesses de fonctionnement dépassant les 10 gigabits par seconde, offrant des améliorations de bande passante qui pourraient augmenter les performances des services d'IA jusqu'à 69 %.

Le « mur de la mémoire » décrit un goulot d'étranglement fondamental dans l'architecture informatique, représentant l'écart de performance croissant entre des processeurs de plus en plus rapides et des temps d'accès mémoire beaucoup plus lents. Cette disparité signifie que les CPU passent fréquemment du temps à attendre les données de la mémoire principale, limitant considérablement la performance globale du système malgré les améliorations continues de la vitesse des processeurs.

L'architecture qui change tout

Le bond technologique représente plus qu'une simple amélioration incrémentale. En doublant la largeur de l'interface d'entrée/sortie de 1 024 à 2 048 bits – la première expansion de ce type depuis la transition de la HBM1 à la HBM2 – SK Hynix a fondamentalement redéfini l'économie du calcul d'IA. Chaque pile de mémoire peut désormais théoriquement délivrer plus de 2,5 téraoctets par seconde de bande passante tout en consommant 40 % moins d'énergie par bit que les générations précédentes.

Comparaison de la bande passante et des fonctionnalités entre les générations HBM (HBM, HBM2, HBM3, HBM4).

| Génération HBM | Année de standardisation/lancement | Débit de données par broche (Gb/s) | Bande passante par pile (Go/s) | Capacité max. par pile (Go) | Largeur d'interface (bits) | Canaux |

|---|---|---|---|---|---|---|

| HBM | 2013 | 1.0 | 128 | 4 | 1024 | 8 |

| HBM2 | 2016 | 2.0 | 256 | 8 | 1024 | 8 |

| HBM2E | 2019 | 3.6 | 461 | 16 | 1024 | 8 |

| HBM3 | 2022 | 6.4 | 819 | 24 (jusqu'à 64 pour pile 16-Hi) | 1024 | 16 |

| HBM3E | 2023 | 9.8 | 1229 | 48 | 1024 | 16 |

| HBM4 | 2025 (Projeté) | 8 (Projeté) | 1600 (Projeté, 1.6 To/s) | 36-64 (Projeté) | 2048 (Projeté) | 32 (Projeté) |

« Ce n'est pas seulement une mémoire plus rapide ; c'est une catégorie différente d'architecture mémoire », note un analyste des semi-conducteurs familier avec le développement. « Le doublement de la largeur force chaque autre composant du système — contrôleurs, interposeurs, alimentation électrique — à être repensé autour de l'implémentation de SK Hynix. »

L'entreprise a réalisé cette percée grâce à ce qu'elle appelle la technologie d'encapsulage Advanced MR-MUF, un processus sophistiqué qui empile jusqu'à 12 puces mémoire tout en gérant la dissipation thermique et l'intégrité structurelle. Contrairement à ses concurrents qui misent sur des processus de fabrication de pointe, SK Hynix a opté pour le nœud DRAM éprouvé de 1b-nanomètre, privilégiant le rendement de fabrication et la fiabilité par rapport aux revendications de performances extraordinaires.

La course contre l'horloge de la demande de la Silicon Valley

Le moment ne pouvait pas être plus critique. La plateforme Rubin de nouvelle génération de NVIDIA, attendue en 2026, est conçue autour des spécifications HBM4. Avec des coûts de formation en IA se mesurant en millions de dollars par modèle et des opérateurs de centres de données confrontés à des factures d'électricité qui grimpent en flèche, l'efficacité de la mémoire est devenue le facteur déterminant dans l'économie de l'intelligence artificielle.

Samsung, qui échantillonne actuellement la HBM4 avec des plans de fourniture pour 2026, a plusieurs mois de retard sur SK Hynix – une éternité dans le cycle rapide du matériel d'IA. Micron, le géant américain de la mémoire, ne commencera pas d'échantillonnage sérieux avant le quatrième trimestre 2025, concédant ainsi le marché précoce à ses concurrents asiatiques.

Des sources industrielles suggèrent que l'avance technique de SK Hynix est plus profonde qu'un simple avantage de calendrier. L'entreprise a déjà livré à ses clients des piles mémoire fonctionnelles à 12 niveaux, prouvant que les défis thermiques et mécaniques de la densité mémoire extrême peuvent être résolus à l'échelle de la production. Les concurrents restent largement en phase de prototype, validant les fonctionnalités de base plutôt que de démontrer la préparation à la fabrication.

Le goulot d'étranglement au-delà de la mémoire

Pourtant, même des puces mémoire parfaites sont confrontées à des contraintes d'infrastructure qui pourraient limiter leur impact à court terme. La capacité d'encapsulage avancée de TSMC, essentielle pour assembler des accélérateurs d'IA complets, reste le goulot d'étranglement de l'industrie. La technologie d'encapsulage « Super Carrier » de nouvelle génération de la fonderie, capable de prendre en charge 12 piles HBM4 par processeur, ne sera qualifiée qu'en 2027.

Cela crée une dynamique inhabituelle où les fournisseurs de mémoire doivent aligner leur production sur la disponibilité de l'encapsulage plutôt que sur les seuls signaux de demande. Les dirigeants de l'industrie reconnaissent en privé que 2026 verra des volumes d'accélérateurs d'IA contraints, quelle que soit la disponibilité des puces mémoire, ce qui pourrait prolonger la fenêtre concurrentielle de SK Hynix.

Cette contrainte explique également pourquoi SK Hynix a choisi des approches de fabrication conservatrices plutôt que des objectifs de performance agressifs. Avec une capacité d'encapsulage limitée, la prime revient aux fournisseurs qui peuvent garantir le rendement et la fiabilité plutôt qu'à ceux qui recherchent des victoires sur les benchmarks.

CoWoS, ou Chip-on-Wafer-on-Substrate, est une technologie d'encapsulage avancée développée par TSMC. Elle permet l'empilement vertical de puces, offrant une plus grande intégration et des performances accrues par rapport au placement traditionnel des puces côte à côte.

Implications pour les investissements : au-delà du cycle de la mémoire

Pour les investisseurs, le leadership de SK Hynix en matière de HBM4 représente un changement fondamental, passant d'une dynamique de mémoire cyclique à une croissance structurelle. Les marchés traditionnels de la DRAM montent et descendent avec les cycles des PC et des smartphones, créant des schémas de boom-bust prévisibles. La demande de mémoire pour l'IA suit les cycles de dépenses en capital des centres de données – mesurés en années plutôt qu'en trimestres et déterminés par la capacité technologique plutôt que par le comportement de remplacement des consommateurs.

L'approche de l'entreprise en matière de dies de base spécifiques aux clients crée des avantages concurrentiels supplémentaires. Contrairement à la mémoire standard qui peut être facilement substituée, les puces HBM4 intègrent de plus en plus une logique personnalisée conçue pour des accélérateurs d'IA spécifiques. Cela fidélise les clients et soutient une tarification basée sur la valeur qui peut persister même lorsque les coûts de fabrication diminuent.

Les études de marché suggèrent que la demande de HBM augmentera d'environ 30 % par an jusqu'en 2030, avec des volumes unitaires pouvant être multipliés par 15 d'ici 2035. Contrairement aux super-cycles mémoire précédents, dictés par des déséquilibres temporaires, la demande de mémoire pour l'IA reflète des exigences architecturales permanentes pour les charges de travail d'apprentissage automatique.

Croissance projetée du marché mondial de la mémoire à haute bande passante (HBM) jusqu'en 2030.

| Année | Taille du marché (milliards USD) | TCAC (%) | Source |

|---|---|---|---|

| 2023 | 1,768 | - | |

| 2024 | 2,5 - 2,9 | - | |

| 2025 | 3,0 - 4,03 | 27,3% (à partir de 2024) | |

| 2030 | 9,2 - 85,75 | 24,2% - 68,1% (à partir de 2024/2023) |

La carte géopolitique de la mémoire

Le leadership technique de SK Hynix a également des implications stratégiques, la mémoire devenant centrale pour la compétitivité nationale en matière d'IA. Les contrôles à l'exportation américains sur les semi-conducteurs avancés ont créé des exigences de conformité complexes, tandis que les entreprises chinoises recherchent des alternatives nationales pour réduire leur dépendance vis-à-vis des fournisseurs étrangers.

La capacité de l'entreprise à servir à la fois les marchés occidentaux et orientaux – tout en maintenant une avance technologique sur ses concurrents chinois nationaux – la positionne pour bénéficier d'une diversification géographique même si les tensions géopolitiques s'intensifient. Cependant, cela crée également des risques réglementaires qui pourraient limiter l'accès aux clients ou forcer des changements opérationnels.

Les analystes de l'industrie suggèrent que les fournisseurs de mémoire dotés de capacités avancées éprouvées pourraient subir une pression croissante pour s'aligner sur des blocs géopolitiques spécifiques, fragmentant potentiellement le marché mondial. Le leadership technique actuel de SK Hynix offre des options, mais les futures décisions politiques pourraient imposer des choix stratégiques difficiles.

Ce que les investisseurs devraient surveiller

Les investisseurs suivant la trajectoire commerciale de la HBM4 devraient se concentrer sur trois métriques critiques : la conversion des revenus contrainte par l'encapsulage, l'atteinte du mix de bacs de vitesse et les risques de concentration des clients. Le pourcentage de production expédiée à des vitesses de 10 gigabits et plus indiquera si les revendications de performance de SK Hynix se traduisent en réalité de fabrication.

Les réservations de capacité d'encapsulage CoWoS par les principaux clients fournissent des indicateurs avancés du potentiel de revenus pour 2026, tandis que les progrès sur les rendements des piles à 12 niveaux déterminent la durabilité de la marge bénéficiaire. Toute diversification au-delà de NVIDIA en tant que client dominant réduirait le risque de concentration et démontrerait une acceptation plus large du marché.

La thèse d'investissement plus large repose sur le maintien des trajectoires de croissance actuelles des dépenses d'infrastructure d'IA. Si les coûts de formation des modèles devaient stagner ou si les contraintes énergétiques forçaient des retards dans la construction de centres de données, même une technologie mémoire supérieure ferait face à des vents contraires de la demande qui pourraient exercer une pression sur les prix et les taux d'utilisation.

Néanmoins, les preuves actuelles suggèrent que SK Hynix a conçu la solution mémoire dont l'IA a désespérément besoin – précisément au moment où l'industrie peut payer des prix élevés pour la performance et la fiabilité. Dans la course aux enjeux élevés pour alimenter l'intelligence artificielle, le timing pourrait s'avérer aussi précieux que la technologie elle-même.

Thèse d'investissement interne

| Catégorie | Résumé et points clés | Évaluation Qualité/Avantage concurrentiel | Calendrier | Risques et atténuateurs |

|---|---|---|---|---|

| Synthèse exécutive | Développement HBM4 terminé ; ligne de production de masse prête. Piles à 12 niveaux échantillonnées en mars 2025. L'innovation clé est l'E/S 2 048 bits (contre 1 024 bits), doublant la largeur du bus et augmentant les coûts de commutation. >10 Gb/s/broche et >40% de gain d'efficacité énergétique ciblent le mur de la mémoire de l'IA. Pas de substitut à court terme. | Leadership en exécution. Avantage concurrentiel grâce au doublement de la largeur et à la fidélisation des clients. Assure une probabilité de >55% de part de marché pour SK Hynix jusqu'en 2026. | 2026 est l'année d'inflexion des revenus pour la HBM4. 2025 est la phase de validation/pré-construction à faible volume. | La capacité d'encapsulage (interposeur/substrat), et non la production de puces, est la contrainte principale. |

| Nouveautés | Bus 2 048 bits et >10 Gb/s/broche (~2,0–2,56 To/s par pile). Utilise DRAM 1b-nm + MR-MUF Avancé pour de meilleurs rendements/thermiques. Les dies de base personnalisés pour les clients clés (par ex. NVIDIA) augmentent la friction de commutation. | Approche pragmatique processus/encapsulage axée sur la « capacité de livraison ». La personnalisation crée un avantage concurrentiel et soutient une tarification basée sur la valeur. | Les dies de base personnalisés fidélisent les clients leaders à moyen terme. | Concurrents développant leurs propres solutions personnalisées. |

| Marché et économie | TCAC de la demande HBM ~30% jusqu'en 2030. Les accélérateurs 2026 (NVIDIA Rubin) utiliseront la HBM4. Les prix de vente moyens et les marges brutes restent élevés en raison de la tarification basée sur la valeur, mais les Capex/COGS augmentent. La discipline de l'offre due aux contraintes d'encapsulage réduit le risque de guerre des prix. | Le % de marge brute HBM4 devrait être > au % de marge brute HBM3E pour SK Hynix. La surabondance de HBM3E a un impact limité sur la rareté de HBM4. | Le « Super Carrier » à 9 réticules de TSMC pour 12 piles HBM4 ne sera qualifié qu'en 2027, limitant les topologies extrêmes jusque-là. | Le goulot d'étranglement de l'encapsulage (CoWoS, approvisionnement en substrat) limite le potentiel de hausse à court terme. |

| Bilan concurrentiel | SK Hynix : N°1 en part de marché et fiabilité. Premier à achever le développement et prêt pour la production de masse. Samsung : N°2 crédible ; échantillons HBM4 disponibles ; plans d'approvisionnement pour 2026 ; rendements en amélioration. Micron : Expédie des échantillons ; sockets sélectifs ; troisième fournisseur à moins d'une victoire majeure. | SK Hynix dispose de l'encapsulage le meilleur de sa catégorie et d'un ancrage chez NVIDIA. Samsung réduit l'écart. Micron est compétitif en termes de perf/W mais est n°3. | Plans d'approvisionnement pour 2026 confirmés par tous. La course porte sur les livraisons d'accélérateurs de première vague en 2026 et la stabilité des bacs de vitesse. | Un rattrapage plus rapide que prévu de Samsung/Micron sur le rendement/thermiques pourrait leur permettre de regagner des parts. |

| Risques clés | 1. Intégration au niveau système : Le timing PHY, les thermiques peuvent forcer des bacs de vitesse inférieurs. Atténuateur : IP de contrôleur (par ex. Rambus) validé jusqu'à 10 Gb/s. 2. Débit/rendement d'encapsulage : Le CoWoS de TSMC est un goulot d'étranglement. 3. Géopolitique : Contrôles à l'exportation américains sur la Chine. 4. Rattrapage des concurrents. | Les risques sont liés à des contraintes techniques et de chaîne d'approvisionnement, et non à la viabilité du produit. | Les risques affectent principalement le calendrier de montée en puissance du premier semestre 2026 et le mélange de bacs de vitesse. | |

| Déclencheurs baissiers | Changement de thèse si : des problèmes de fiabilité du 12-Hi forcent des déclassements de vitesse ; les accélérateurs 2026 choisissent des configurations HBM3E/HBM4 mixtes en raison de la rareté de l'encapsulage ; un concurrent décroche un socket principal avant que SK Hynix n'atteigne des bacs stables à 10 Gb/s. | Ces événements indiqueraient un échec d'exécution technique ou un changement dans le paysage concurrentiel. | Retarderait l'inflexion des revenus HBM4 en 2026 et le changement de mix. | |

| Positionnement et ICP | Investisseurs haussiers SK Hynix : Confirmation d'un avantage concurrentiel durable et d'une hausse des bénéfices en 2026. Suivre le mélange/rendement des bacs de vitesse et les revenus contraints par l'encapsulage. Pairs : Doivent démontrer une stabilité de 10 Gb/s d'ici mi-2026 pour éviter d'être des preneurs de prix. | ICP : % de production de masse à ≥10 Gb/s ; rendement 12-Hi ; capacité CoWoS réservée ; part des livraisons de dies de base personnalisés ; rapports d'acceptation des clients clés. | Calendrier clé pour la validation : mise en service des premiers siliciums pour les puces 2026 (Rubin). | |

| En résumé | Ingénierie excellente et commercialement décisive. Le doublement de la largeur + >10 Gb/s + un encapsulage éprouvé + la relation avec NVIDIA devraient maintenir SK Hynix en tête jusqu'en 2026. La limite principale est la capacité d'encapsulage, pas la disponibilité du dispositif. | Soutient un leadership continu en parts de marché et une surperformance des marges en HBM. | Les surprises de validation/rendement pourraient freiner la montée en puissance du premier semestre 2026. |

Les décisions d'investissement doivent tenir compte de la tolérance au risque individuelle et des conseils financiers professionnels. Les performances passées des actions technologiques ne garantissent pas les résultats futurs.